V předchozí kapitole jsme se zabývali západkami. To jsou základní stavební kameny klopných obvodů. Flip-flopy můžeme implementovat dvěma způsoby.

Při prvním způsobu kaskádujeme dva latche tak, že první latch je aktivován při každém kladném hodinovém impulsu a druhý latch je aktivován při každém záporném hodinovém impulsu. Tak se z kombinace těchto dvou západek stane flip-flop.

Při druhém způsobu můžeme přímo implementovat flip-flop, který je citlivý na hrany. V této kapitole probereme následující flip-flopy využívající druhou metodu.

- SR Flip-Flop

- D Flip-Flop

- JK Flip-Flop

- T Flip-Flop

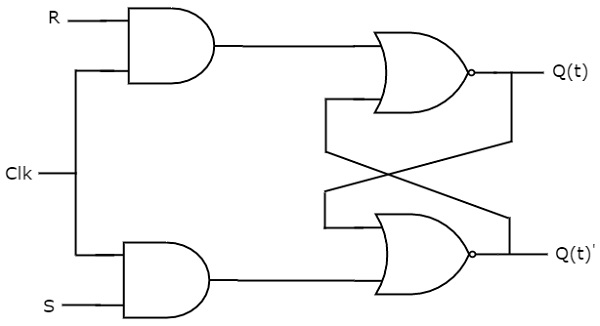

SR Flip-Flop

SR flip-flop pracuje pouze s kladnými nebo zápornými hodinovými přechody. Zatímco SR západka pracuje s povolovacím signálem. Schéma zapojení SR flip-flopu je znázorněno na následujícím obrázku.

Tento obvod má dva vstupy S & R a dva výstupy Q(t) & Q(t)’. Činnost SR flipflopu je podobná jako u SR Latch. Tento flip-flop však ovlivňuje výstupy pouze při kladném přechodu hodinového signálu místo aktivního povolení.

Následující tabulka ukazuje stavovou tabulku SR flip-flopu.

| S | R | Q(t + 1) |

|---|---|---|

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | – |

Tady, Q(t) & Q(t + 1) jsou současný stav & resp. následující stav. Takže SR flip-flop může být použit pro jednu z těchto tří funkcí, jako je Hold, Reset & Set na základě vstupních podmínek, když je přiveden kladný přechod hodinového signálu. Následující tabulka ukazuje tabulku charakteristik SR flip-flopu.

| Aktuální vstupy | Aktuální stav | Následující stav | |

|---|---|---|---|

| S | R | Q(t) | Q(t + 1) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | x |

| 1 | 1 | 1 | x |

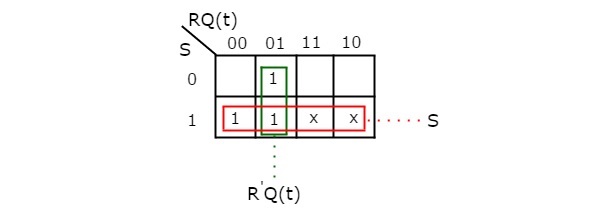

Pomocí tří proměnných K-.Map, můžeme získat zjednodušený výraz pro další stav Q(t + 1). Tříproměnná K-mapa pro další stav, Q(t + 1), je znázorněna na následujícím obrázku.

Na obrázku jsou již znázorněna maximální možná seskupení sousedních. Zjednodušený výraz pro další stav Q(t + 1) je tedy

$Q\left ( t+1 \right )=S+{R}’Q\left ( t \right )$

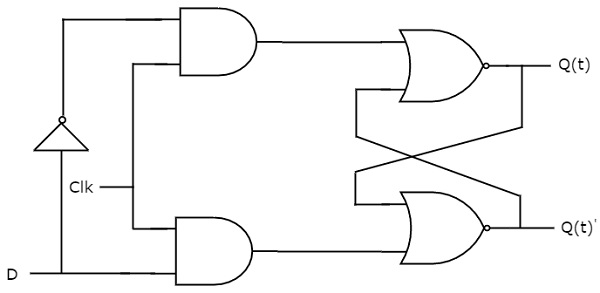

D flip-flop

D flip-flop pracuje pouze s kladnými nebo zápornými hodinovými přechody. Zatímco D západka pracuje s povolovacím signálem. To znamená, že výstup D klopného obvodu je necitlivý na změny na vstupu D s výjimkou aktivního přechodu hodinového signálu. Schéma zapojení D klopného obvodu je znázorněno na následujícím obrázku.

Tento obvod má jeden vstup D a dva výstupy Q(t) & Q(t)’. Činnost D flip-flopu je podobná jako u D Latch. Tento flip-flop však ovlivňuje výstupy pouze při kladném přechodu hodinového signálu místo aktivního povolení.

Následující tabulka ukazuje stavovou tabulku D flip-flopu.

| D | Qt + 1t + 1 |

|---|---|

| 0 | 0 |

| 1 | 1 |

Takže, D flip-flop vždy podrží informaci, která je k dispozici na datovém vstupu, D dřívějšího kladného přechodu hodinového signálu. Z výše uvedené stavové tabulky můžeme přímo zapsat rovnici dalšího stavu jako

Q(t + 1) = D

Následující stav D klopného obvodu je vždy roven datovému vstupu, D pro každý kladný přechod hodinového signálu. Proto lze D flip-flop použít v registrech, posuvných registrech a některých čítačích.

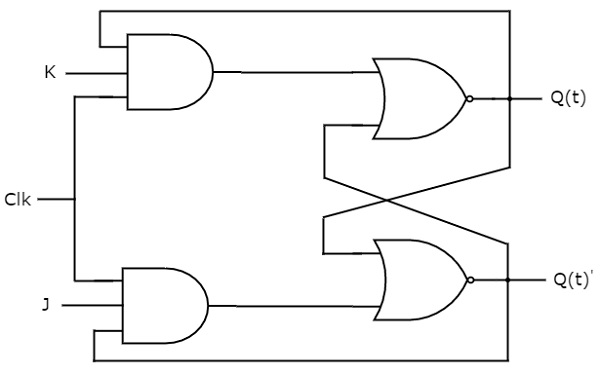

JK flip-flop

JK flip-flop je modifikovaná verze SR flip-flopu. Pracuje pouze s kladnými nebo zápornými hodinovými přechody. Schéma zapojení JK flip-flopu je znázorněno na následujícím obrázku.

Tento obvod má dva vstupy J & K a dva výstupy Q(t) & Q(t)’. Činnost JK flip-flopu je podobná jako u SR flip-flopu. Zde jsme uvažovali vstupy SR flip-flopu jako S = J Q(t)’ a R = KQ(t), abychom mohli využít modifikovaný SR flip-flop pro 4 kombinace vstupů.

Následující tabulka ukazuje stavovou tabulku JK flip-flopu.

| J | K | Q(t + 1) |

|---|---|---|

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Q(t)’ |

Zde, Q(t) & Q(t + 1) jsou současný stav & resp. následující stav. JK flip-flop lze tedy použít pro jednu z těchto čtyř funkcí, jako je Hold, Reset, Set & Doplněk současného stavu na základě vstupních podmínek, když je přiveden kladný přechod hodinového signálu. V následující tabulce je uvedena tabulka charakteristik JK flip-flopu.

| Aktuální vstupy | Aktuální stav | Následující stav | |

|---|---|---|---|

| J | K | Q(t) | Q(t+1) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

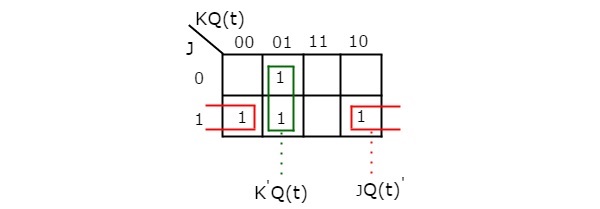

Pomocí tří proměnných K-.Map, můžeme získat zjednodušený výraz pro další stav Q(t + 1). Tříproměnná K-mapa pro další stav, Q(t + 1), je znázorněna na následujícím obrázku.

Maximální možná seskupení sousedních jsou již znázorněna na obrázku. Zjednodušený výraz pro další stav Q(t+1) je tedy

$$Q\left ( t+1 \right )=J{Q\left ( t \right )}’+{K}’Q\left ( t \right )$$

T flip-flop

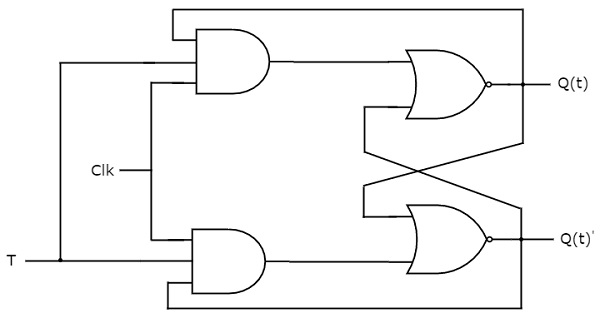

T flip-flop je zjednodušená verze JK flip-flopu. Vznikne připojením stejného vstupu ‘T’ na oba vstupy JK flip-flopu. Pracuje pouze s kladnými nebo zápornými hodinovými přechody. Schéma zapojení T flip-flopu je znázorněno na následujícím obrázku.

Tento obvod má jeden vstup T a dva výstupy Q(t) & Q(t)’. Činnost T klopného obvodu je stejná jako u JK klopného obvodu. Zde jsme uvažovali vstupy JK flip-flopu jako J = T a K = T, abychom mohli využít modifikovaný JK flip-flop pro 2 kombinace vstupů. Vyloučili jsme tedy další dvě kombinace J & K, pro které se tyto dvě hodnoty v T flip-flopu vzájemně doplňují.

Následující tabulka ukazuje stavovou tabulku T flip-flopu.

| D | Q(t + 1) |

|---|---|

| 0 | Q(t) |

| 1 | Q(t)’ |

Zde, Q(t) & Q(t + 1) jsou současný stav & resp. následující stav. T flip-flop lze tedy použít pro jednu z těchto dvou funkcí, jako je Hold, & Doplnění současného stavu na základě vstupních podmínek, když je přiveden kladný přechod hodinového signálu. V následující tabulce je uvedena tabulka charakteristik T flip-flopu.

| Vstupy | Aktuální stav | Následující stav |

|---|---|---|

| T | Q(t) | Q(t + 1) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Z výše uvedené tabulky charakteristik, můžeme přímo zapsat další stavovou rovnici jako

$$Q\left ( t+1 \right )={T}’Q\left ( t \right )+TQ{\left ( t \right )}’$$

$\Pravá šipka Q\left ( t+1 \right )=T\oplus Q\left ( t \right )$$

Výstup T flip-flopu se vždy přepne při každém kladném přechodu hodinového signálu, když na vstupu T zůstává logická hodnota High (1). Proto lze T flip-flop použít v čítačích.

V této kapitole jsme implementovali různé flip-flopy zajištěním křížové vazby mezi hradly NOR. Podobně můžete tyto klopné obvody realizovat pomocí hradel NAND.

.